在一個晶圓上,通常有幾百個至數千個芯片連在一起。它們之間留有80um至150um的間隙,此間隙被稱之為劃片街區(Saw Street)。將每一個具有獨立電氣性能的芯片分離出來的過程叫做劃片或切割(Dicing Saw)。目前,機械式金剛石切割是劃片工藝的主流技術。在這種切割方式下,金剛石刀片(Diamond Blade)以每分鐘3萬轉到4萬轉的高轉速切割晶圓的街區部分,同時,承載著晶圓的工作臺以一定的速度沿刀片與晶圓接觸點的切線方向呈直線運動,切割晶圓產生的硅屑被去離子水(DI water)沖走。依能夠切割晶圓的尺寸 ,目前半導體界主流的劃片機分8英寸晶圓和12英寸晶圓劃片機兩種。

晶圓劃片工藝的重要質量缺陷的描述

崩角 (Chipping)

因為硅材料的脆性,機械切割方式會對晶圓的正面和背面產生機械應力,結果在芯片的邊緣產生正面崩角(FSC- Front Side Chipping)及背面崩角(BSC – Back Side Chipping)。

正面崩角和背面崩角會降低芯片的機械強度,初始的芯片邊緣裂隙在后續的封裝工藝中或在產品的使用中會進一步擴散,從而可能引起芯片斷裂,導 致電性失效。另外,如果崩角進入了用于保護芯片內部電路、防止劃片損傷的密封環(Seal Ring)內部時,芯片的電氣性能和可靠性都會受到影響。

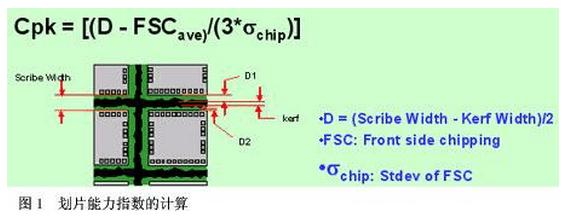

封裝工藝設計規則限定崩角不能進入芯片邊緣的密封圈。如果將崩角大小作為評核晶圓切割質量/能力的一個指標,則可用公式來計算晶圓切割能力指數(Cpk)(圖1)。

D1、D2代表劃片街區中保留完整的部分,FSC是指正面崩角的大小。依照封裝工藝設計規則,D1、D2的最小值可以為0,允許崩角存在的區域寬度D為(街區寬度-刀痕寬度)/2, 為D1、D2的平均值, 為D1、D2的方差。依統計學原理,對于一個合格的劃片工藝而言,其切割能力指數應大于1.5。

分層與剝離(Delamination & Peeling)

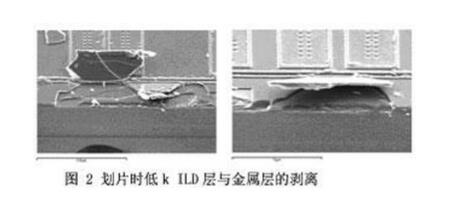

由于低k ILD層獨特的材料特性,低k晶圓切割的失效模式除了崩角缺陷外,芯片邊緣的金屬層與ILD層的分層和剝離是另一個主要缺陷(圖2)。

對于低k晶圓切割質量評估,除了正面崩角和背面崩角以外,根據實驗數據和可靠性結果,規定了下述切割質量指標:

(1)銅密封環不允許出現斷裂,分層或其他任何(在200倍顯微鏡下)可見的損傷。

(2)在劃片街區上出現金屬與ILD層的分層是允許的,只要這種分層能止步于銅密封環外。

(3)在芯片的頂角區域的金屬/ILD層不允許出現分層或損傷,唯一的例外是有封裝可靠性數據證明在某種特定的芯片設計/封裝結構的組合下芯片的頂角區域的損傷可以接受。

圖3給出了低k晶圓切割質量拒收標準的示例。

影響晶圓劃片質量的重要因素

劃片工具,材料及劃片參數

劃片工具和材料主要包括:劃片刀(Dicing blade)、承載薄膜(Mounting tape), 劃片參數主要包括:切割模式、切割參數(步進速度、刀片轉速、切割深度等)。對于由不同的半導體工藝制作的晶圓需要進行劃片工具的選擇和參數的優化,以達到最佳的切割質量和最低的切割成本。

切割街區的測試圖案

在晶圓的制造過程中,為了獲得較高的成品率、較低的制造成本和穩定的工藝制程,每一步工藝都處于嚴格的監控下。因此,測試

圖案被設計出來并對其進行監測,以確保關鍵參數如電參數、制程精度如ILD層/金屬層的淀積厚度、掩膜對準精度及金屬線寬容差等滿足設計要求。通常有3種方式來實現晶圓工藝制程監控:

(1)離線測試,這種測試將所有的測試圖案放入被稱為―工藝確認晶圓‖(PVW – Process Validation Wafer)的特別設計的晶圓上。優點是可以包括所有需要測試的圖案,因而可以執行一個全面的工藝制程監控;缺點是高成本和費時。它通常應用在產品的研發初期。當產品技術日趨成熟后,這種測試方法會被其他的測試方法所取代。

(2)測試芯片插入法。所有的測試圖案被放入測試芯片內,這些測試芯片被安放在晶圓上的不同區域。測試芯片的數目和位置取決于晶圓制造技術的復雜度。優點是它是一種實時監控。如果某種致命的缺陷發生在晶圓制造流程的早期,就可以避免由于整個晶圓報廢而帶來的損失。這種測試方法的缺點是它占用了寶貴的硅片資源,尤其是當單個芯片尺寸較大,而PDPW(Potential Die Per Wafer)數目較小的時候。

(3)周邊測試,測試圖案被放置在劃片街區內(圖4)。將測試圖案放在劃片街區內能夠在實現實時監控的同時,節約了寶貴的硅片資源。可以放進劃片街區的測試圖案的數目取決于在一個掩膜(Reticle)內劃片街區的長度和面積。在一個Reticle內劃片街區上的測試圖案,會隨著步進式光刻的進行,在整個晶圓上得到復制。在Reticle內部,所有的測試圖案都是唯一的,互不相同。而在不同的Reticle之間,測試圖案是重復的。